![[전문서적] 디지털 논리회로](/_files/goods/202409/20240927111221.jpg)

[전문서적] 디지털 논리회로

30,000원

예상적립포인트 : 300P

- 모델코드

- TWS003

- 배송안내

상세정보

디지털 논리회로

- 김종현

- 생능출판사

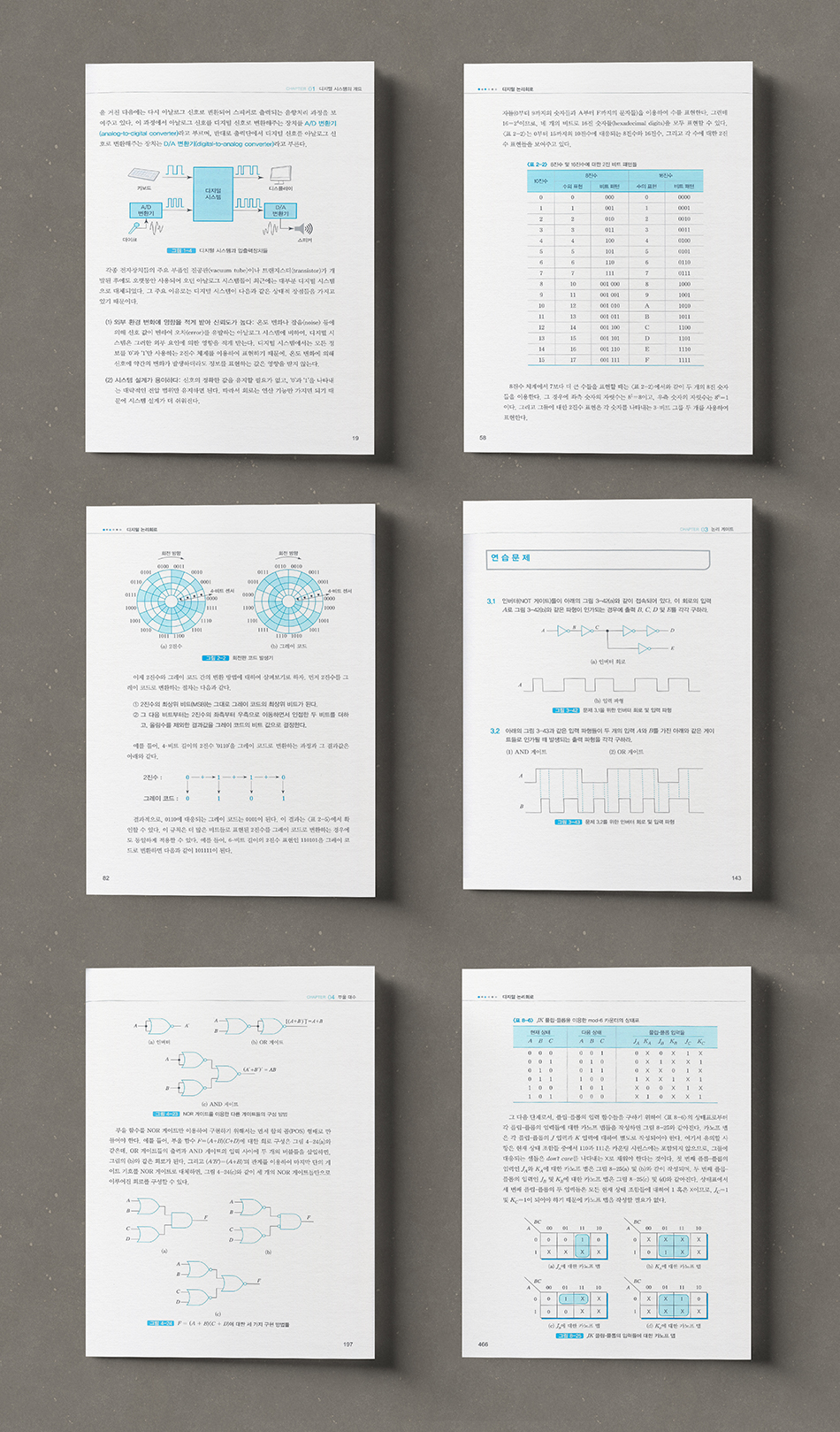

- 논리회로의 분석 및 설계를 위하여 반드시 알아야 할 핵심적인 내용들만 발췌하여 이해하기 쉽도록 간결하게 설명하였다.

- 각 장에는 본문의 내용을 학습한 뒤 풀 수 있는 연습문제를 수록함으로써 개념을 명확하게 이해하는데 도움이 되도록 하였다.

목차

- Chapter 1.디지털 시스템의 개요

-

- 1.1 아날로그 신호와 디지털 신호

- 1.2 아날로그 시스템과 디지털 시스템

- 1.3 디지털 정보의 표현

- 1.4 디지털 논리 연산의 개념

- 1.5 논리게이트

- 1.6 조합회로 및 순차회로

- 1.7 디지털 IC 칩

- 기본문제

- 연습문제

- Chapter 2.2진수 체계와 디지털 코드

-

- 2.1 2진수 표현

- 2.2 8진수 및 16진수 표현

- 2.3 2진 산술 연산

- 2.4 음수 표현

- 2.5 2의 보수 산술 연산

- 2.6 각종 2진 코드들

- 기본문제

- 연습문제

- Chapter 3.논리 게이트

-

- 3.1 기본 논리게이트

- 3.2 NAND 게이트와 NOR 게이트

- 3.3 Exclusive-OR 게이트

- 3.4 논리게이트의 내부 회로

- 3.4 논리게이트 IC칩을 이용한 회로 구현

- 기본문제

- 연습문제

- Chapter 4.부울 대수

-

- 4.1 부울 연산의 표현

- 4.2 부울 대수의 법칙과 규칙

- 4.3 부울 대수를 이용한 논리회로의 분석

- 4.4 부울 대수를 이용한 논리회로의 설계

- 4.5 표준형 부울 함수의 표현

- 4.6 NAND 및 NOR 게이트를 이용한 회로 구현

- 4.7 XOR 연산과 XNOR 연산

- 기본문제

- 연습문제

- Chapter 5.카노프 맵을 이용한 부울 함수의 간략화

-

- 5.1 3-변수 카노프 맵

- 5.2 4-변수 카노프 맵

- 5.3 셀의 인접성을 이용한 간략화 방법

- 5.4 POS 표현의 간략화

- 5.5 POS 표현과 SOP 표현 간의 변환

- 5.6 Don’t Care 조건을 가진 경우의 간략화

- 5.7 5-변수 카노프 맵

- 5.8 XOR 함수에 대한 카노프 맵

- 기본문제

- 연습문제

- Chapter 6.조합회로의 분석과 설계

-

- 6.1 조합회로의 기본 구조

- 6.2 조합회로의 분석

- 6.3 조합회로의 설계방법

- 6.4 가산기

- 6.5 디코더

- 6.6 엔코더

- 6.7 그레이 코드 변환기

- 6.8 비교기

- 6.9 멀티플렉서

- 6.10 디멀티플렉서

- 6.11 산술연산 회로

- 6.12 패리티 발생기

- 기본문제

- 연습문제

- Chapter 7.순차회로의 분석과 설계

-

- 7.1 래치

- 7.2 플립-플롭

- 7.3 순차회로의 분석

- 7.4 순차회로의 설계

- 기본문제

- 연습문제

- Chapter 8.카운터 및 레지스터

-

- 8.1 비동기식 카운터

- 8.2 동기식 카운터

- 8.3 동기식 카운터의 설계

- 8.4 레지스터

- 기본문제

- 연습문제

- Chapter 9.PLD와 FPGA

-

- 9.1 PLD의 개요

- 9.2 PROM을 이용한 회로 구현

- 9.3 PAL을 이용한 회로 구현

- 9.4 PLA를 이용한 회로 구현

- 9.5 CPLD

- 9.6 FPGA

- 기본문제

- 연습문제

- 부록.실험

-

- 실험 1 : 기본 게이트 회로 시험

- 실험 2 : NAND 게이트 실험

- 실험 3 : Exclusive-OR 게이트 실험

- 실험 4 : 부울 함수의 간략화 표현

- 실험 5 : 산술연산회로 실험

- 실험 6 : 디코더 시험

- 실험 7 : 우선순위 엔코더 시험

- 실험 8 : 순차회로의 분석

- 실험 9 : 비동기식(리플)카운터

- 실험 10 : 동기식 업-다운 카운터